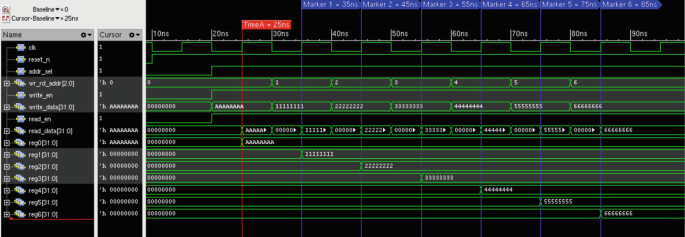

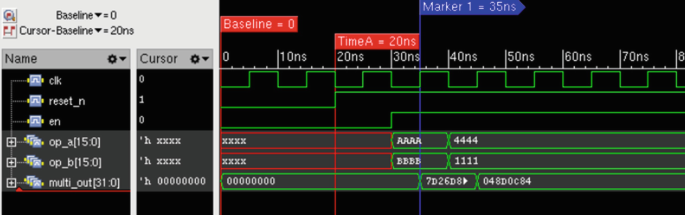

CPE/EE 427, CPE 527, VLSI Design I: Tutorial #4, Standard cell design flow (from verilog to layout, 8-bit accumulator)

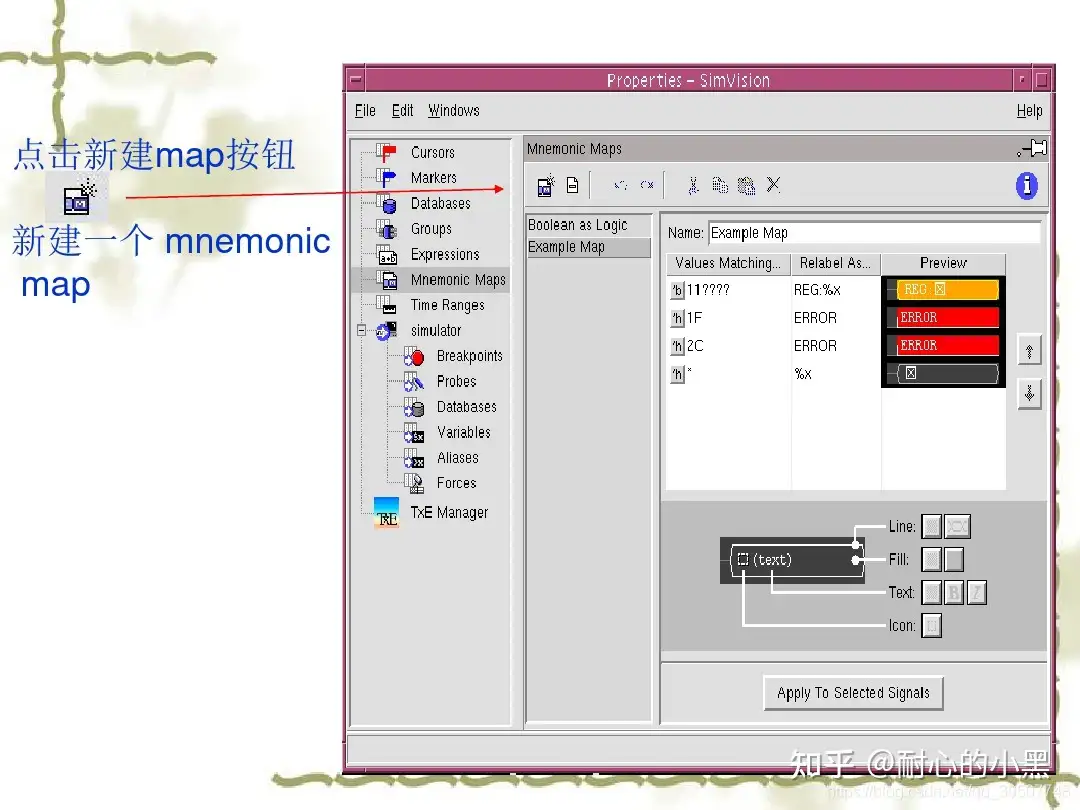

Simvision: Using The Waveform Window: Product Version 15.2 February 2016 | PDF | Window (Computing) | Menu (Computing)

Simvision: Using The Waveform Window: Product Version 15.2 February 2016 | PDF | Window (Computing) | Menu (Computing)

Simvision: Using The Waveform Window: Product Version 15.2 February 2016 | PDF | Window (Computing) | Menu (Computing)

CPE/EE 427, CPE 527, VLSI Design I: Tutorial #3, Standard cell design flow (from schematic to layout, 8-bit accumulator)

Simvision: Using The Waveform Window: Product Version 15.2 February 2016 | PDF | Window (Computing) | Menu (Computing)

How to remove multiple Markers quickly in Simvision? - Functional Verification - Cadence Technology Forums - Cadence Community

CPE/EE 427, CPE 527, VLSI Design I: Tutorial #3, Standard cell design flow (from schematic to layout, 8-bit accumulator)